Registers

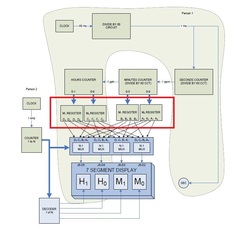

At this point in the project, we have 4 DIP switches connected to our multiplexers, feeding the numbers to be displayed on the 7-segment display. Since we are continuing the process of making a digital clock, we need something to store the numbers to the 7-segment display via logic gate manipulation. This will be done by replacing the switches with 6 registers, or buffers that will store the minute and hour digit values in binary.

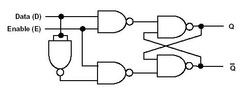

D Flip-Flop

When Enable is 0, both control NAND gates will have a 1 output, and the RS latch will remain stable. When Enable = 1, Q will become equal to Data. If Data changes while Enable = 1, Q will also change. When Enable goes back to 0, the most recent value of D will remain on the Q output, effective storing 1 bit

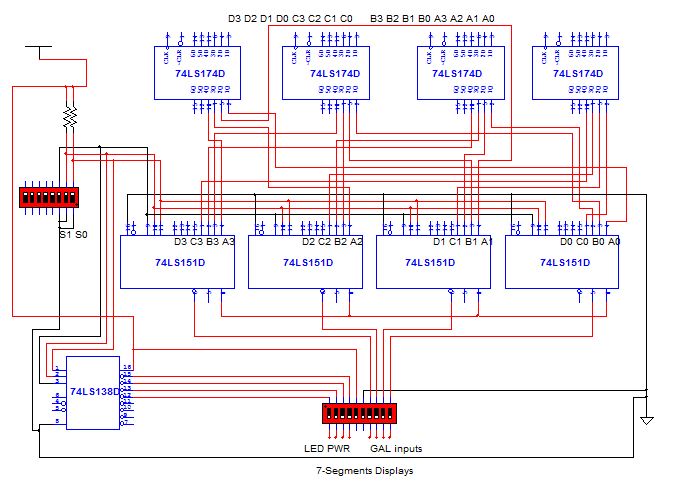

Register System Description

The registers we are using in this project are 4 - 74LS174 Hex D Flip-Flop TTLs. Each register is used to store one digit of the minute-hour clock, provided by the pulses from the divide by circuitry.

The registers are made up of 6 parallel D Flip-Flops. Each flip flop stores one bit of data depending on the input signal and the clock. This means that each one of these devices can hold up to 6 bits of memory. For this project, we only requires 4 bit for each digit, this means the excessive D Flip Flops inputs are to be tied low for 0.

The registers are made up of 6 parallel D Flip-Flops. Each flip flop stores one bit of data depending on the input signal and the clock. This means that each one of these devices can hold up to 6 bits of memory. For this project, we only requires 4 bit for each digit, this means the excessive D Flip Flops inputs are to be tied low for 0.

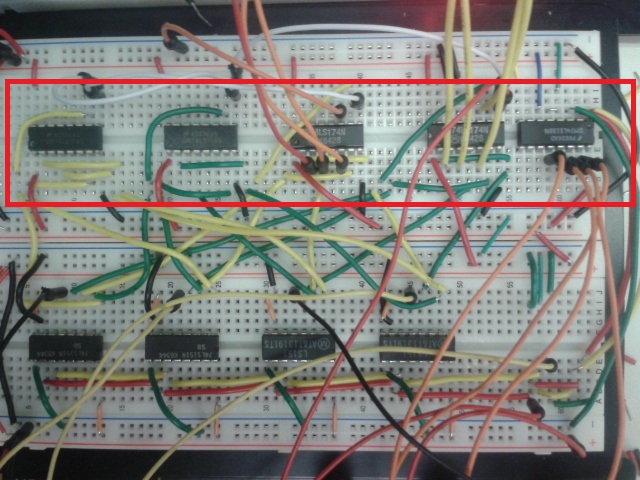

The registers are implemented one at a time to for easier debugging in case of mis-wiring. The registers replaced the switch, and the outputs are wired receptively.

Testing

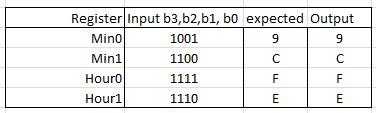

Observe numbers that appear on the 7-segment display as the D flip-flops are hard-wired into ground and power.

Conclusion

The registers worked as expected. However, the tight spacing on the proto-board is getting increasingly difficult to add further wiring and components. The laid could have been neater and that is what we are aiming for in the rest of the project.

There was no problem encounter in this module.

There was no problem encounter in this module.